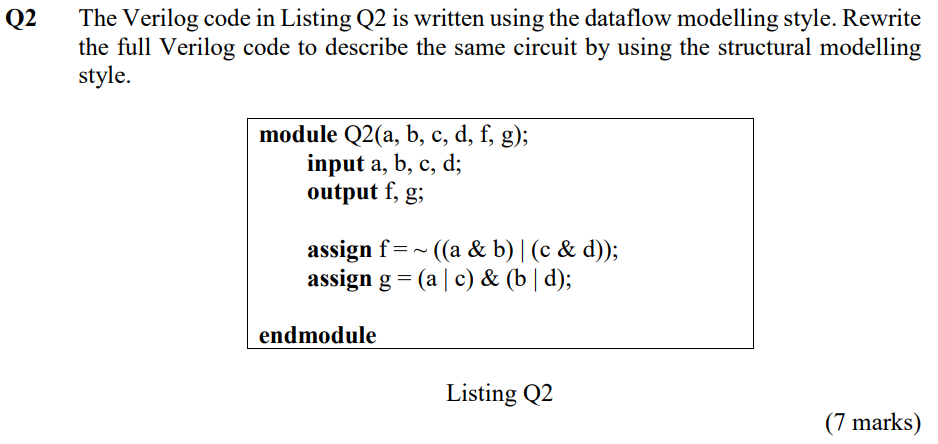

Data Flow Modelling in Verilog

Verilog is a HARDWARE DESCRIPTION LANGUAGE HDL which is used to describe a digital system such as a network switch or a microprocessor or a memory a flip-flop. Module AND_2_data_flow output Y input A B.

Veriloghdl Basic Data Flow Modelling Youtube

The conversion time is maintained constant in successive approximation type ADC and is proportional to the number of bits in the digitaloutput unlike the.

. In succession of International Conferences SPIN-2014 SPIN-2015 SPIN-2016 SPIN-2017 SPIN-2018 SPIN-2019 SPIN-2020 SPIN 2021 9th International Conference on Signal Processing and Integrated Networks SPIN-2022 will be organized by Amity University Noida on 25-26 August 2022. Meanwhile the graphics engine will execute post-processed data from the previous batch dumped into another part of memory and so on. They also decide on how the data should flow inside the chip.

Today Verilog is the most popular HDL used and practiced throughout the semiconductor industry. The concurrent statements in VHDL are WHEN and GENERATE. Ansys Electronics Desktop AEDT The Ansys Electronics Desktop AEDT is a platform that enables true electronics system design.

Week-6Switch level modelling Week-7Synthesis of combinational logic using verilog Week-8Synthesis of sequential logic. Verilog code for AND gate using data-flow modeling. An example would be the data flow when a processor fetches imaging data from the system ram and executes them.

In this modeling style the flow of data through the entity is expressed using concurrent parallel signal. Then we use assignment statements in data flow modeling. Behavioral modeling is the highest level of abstraction in the Verilog HDL.

The VLSI IC circuits design flow is shown in the figure below. Successive Approximation type ADC is the most widely used and popular ADC method. The various levels of design are numbered and the blocks show processes in the design flow.

Verilog was developed to simplify the process and make the HDL more robust and flexible. All that a designer need is the. We would again start by declaring the module.

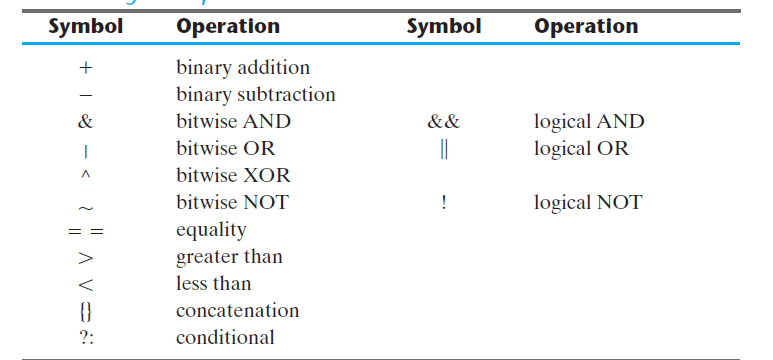

Besides them assignments using only operators AND NOT sll etc can also be used to construct code. AEDT provides access to the Ansys gold-standard electromagnetics simulation solutions such as Ansys HFSS Ansys Maxwell Ansys Q3D Extractor Ansys SIwave and Ansys Icepak using electrical CAD ECAD and mechanical CAD MCAD. A comprehensive resource on Verilog HDL for beginners and experts large and complicated digital circuits can be incorporated into hardware by using Verilog a hardware description language HDL.

Describes how the Vitis development environment lets you build a software application using the OpenCL API to run hardware kernels on accelerator cards like a Xilinx Alveo Data Center accelerator card for FPGA-based acceleration. Specifications comes first they describe abstractly the functionality interface and the architecture of the digital IC circuit to be designed.

Solved The Verilog Code In Listing Q2 Is Written Using The Chegg Com

What Is The Difference Between Data Flow And Behavioral Modelling In Verilog Hdl Ee Vibes

Verilog Part 1 Example Dataflow And Structural Description Youtube

No comments for "Data Flow Modelling in Verilog"

Post a Comment